UNIVERSITY OF ROME "LA SAPIENZA"

INFINEON TECHNOLOGIES AG

Never stop thinking

DEPARTMENT OF ELECTRONIC ENGINEERING

# ACTIVE PROBE CIRCUIT TO IMPLEMENT POWER ANALYSIS TECHNIQUES

Main supervisor University of Rome "La Sapienza": PROF. ALESSANDRO TRIFILETTI

Main supervisor Infineon Technologies AG: DR. DIPL. ING. RAIMONDO LUZZI

Degree Thesis of MICHELE MARINO Student number: 792033

Academic Year 2005 - 2006

Ai miei genitori Salvatore e Teresa che mi hanno sempre sostenuto, e ai miei nipotini Francesco Pio, Alessia e Maria Teresa.

# Contents

| Pı           | efac                      | e                                 | 9  |

|--------------|---------------------------|-----------------------------------|----|

| 1            | Smartcards & Cryptography |                                   |    |

| <b>2</b>     | Att                       | acking techniques                 | 15 |

|              | 2.1                       | Physical Attacks on Smart Cards   | 15 |

|              | 2.2                       | Fault attacks                     | 16 |

|              | 2.3                       | Side-channel attacks              | 16 |

|              |                           | 2.3.1 Timing attacks              | 17 |

|              |                           | 2.3.2 Power Analysis Foundations  | 17 |

|              |                           | 2.3.3 Simple Power Analysis       | 20 |

|              |                           | 2.3.4 Differential power analysis | 21 |

|              | 2.4                       | Countermeasures                   | 26 |

| 3            | Sup                       | ply and Current Measurement Probe | 29 |

|              | 3.1                       | First version: SCM                | 29 |

|              | 3.2                       | Second version: current probe     | 32 |

|              | 3.3                       | Transfer function calculation     | 34 |

|              | 3.4                       | Small signal analysis             | 40 |

|              | 3.5                       | Stability analysis                | 46 |

|              | 3.6                       | S-Parameters measurement          | 56 |

|              | 3.7                       | DPA attack results                | 59 |

| <b>4</b>     | Cor                       | nmon Base Current Probe (CBCP)    | 66 |

|              | 4.1                       | S-Parameters measurement          | 74 |

|              | 4.2                       | DPA Attack Results                | 74 |

| <b>5</b>     | Fea                       | ture comparison                   | 79 |

| 6            | Cor                       | nclusions                         | 81 |

| $\mathbf{A}$ | $\mathbf{TH}$             | S320X internal structure          | 82 |

| $\mathbf{B}$ | Cur            | rent Feedback Amplifier                       | 86  |

|--------------|----------------|-----------------------------------------------|-----|

|              | B.1            | Development of the general feedback equation  | 86  |

|              | B.2            | Current feedback stability equation           | 88  |

|              | B.3            | Developing the non-inverting circuit equation | 90  |

|              | B.4            | Developing the inverting circuit equation     | 91  |

|              | B.5            | Stability analysis                            | 92  |

|              | B.6            | Performance Analysis                          | 97  |

|              | B.7            | CFA summary                                   | 98  |

| С            | S-pa           | arameters measurement                         | 100 |

| D            | MA             | TLAB script for stability analysis            | 103 |

| Bi           | Bibliography 1 |                                               |     |

# List of Figures

| 2.1  | Side-channel attacks diagram                                                                  | 17 |

|------|-----------------------------------------------------------------------------------------------|----|

| 2.2  | CMOS Inverter                                                                                 | 20 |

| 2.3  | SPA trace from a typical smart card during a DES operation $[6]$                              | 20 |

| 2.4  | Detailed view of SPA trace $[6]$                                                              | 21 |

| 2.5  | Detailed view of SPA trace $[6]$                                                              | 22 |

| 2.6  | DES Algorithm                                                                                 | 22 |

| 2.7  | Data Encryption Standard (F-function)                                                         | 24 |

| 2.8  | $DPA$ traces for a DES encryption function [6] $\ldots \ldots \ldots \ldots \ldots$           | 25 |

| 2.9  | Average effect of a single bit on $DPA$ attack [6] $\ldots \ldots \ldots \ldots$              | 26 |

| 3.1  | Current measurement with a resistor-based setup                                               | 29 |

| 3.2  | SCM general circuit                                                                           | 30 |

| 3.3  | Serpent algorithmic                                                                           | 31 |

| 3.4  | Comparison of experimental results obtained with both methods $\ . \ .$                       | 32 |

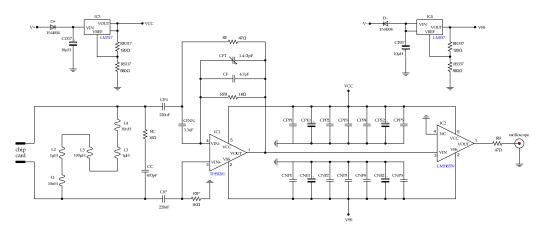

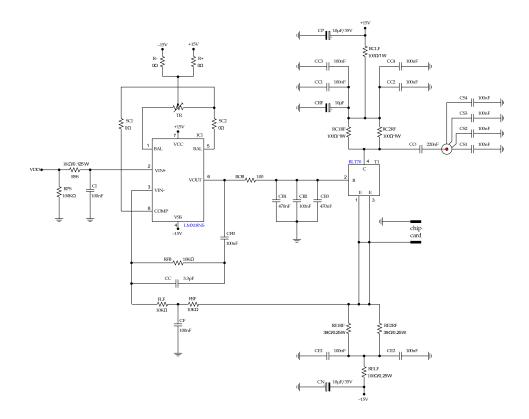

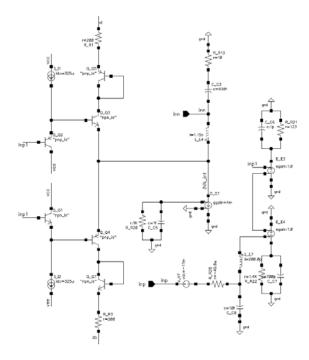

| 3.5  | SCM Schematic of the second version                                                           | 33 |

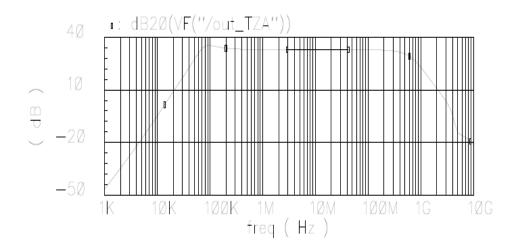

| 3.6  | $AC$ response of the second version $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 34 |

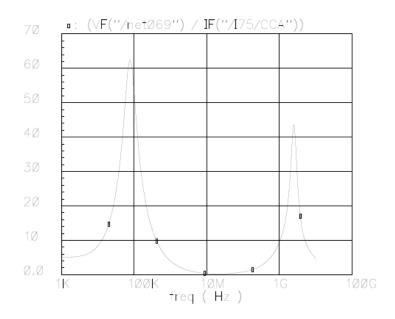

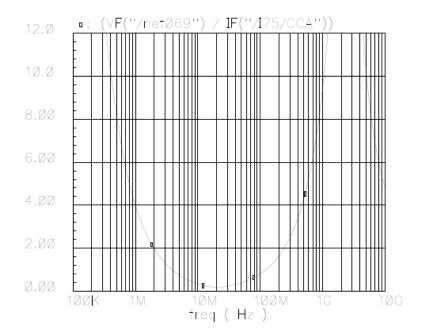

| 3.7  | Input impedance                                                                               | 35 |

| 3.8  | Zoomed input impedance in the useful frequency range                                          | 35 |

| 3.9  | Circuit for calculation of the transfer function                                              | 36 |

| 3.10 | Simplified schematic for transfer function calculation                                        | 36 |

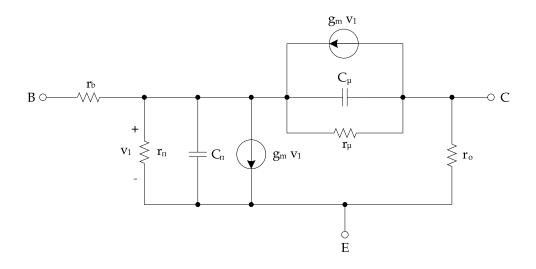

| 3.11 | Small signal circuit for SCM second version                                                   | 41 |

| 3.12 | Block model for the parallel-parallel feedback                                                | 42 |

| 3.13 | Schematic block with load effect in the direct amplification block $\ .$ .                    | 43 |

| 3.14 | Equivalent block diagram for the calculation of the input impedance                           | 45 |

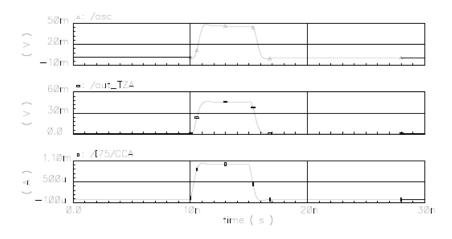

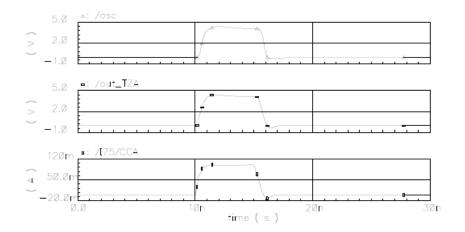

|      | Transient response for $i_p = 1mA$                                                            | 46 |

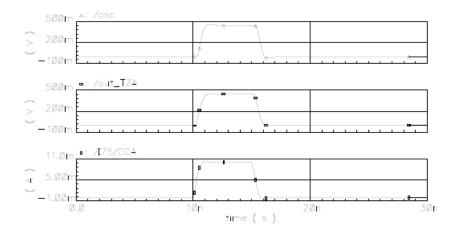

| 3.16 | Transient response for $i_p = 10mA$                                                           | 47 |

|      | Transient response for $i_p = 100mA$                                                          | 47 |

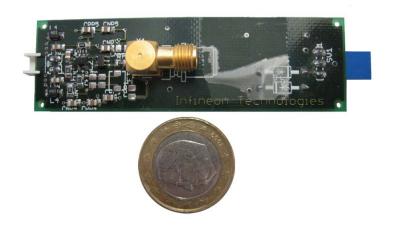

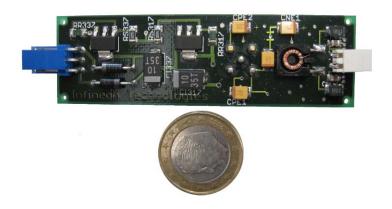

| 3.18 | Front view of SCM second version                                                              | 48 |

| 3.19 | Back view of SCM second version                                                               | 48 |

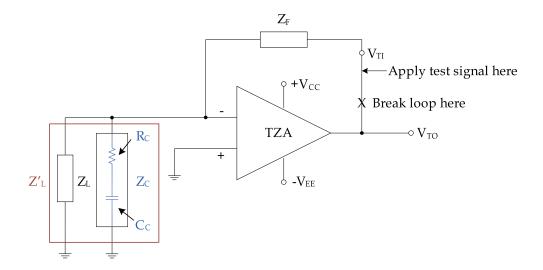

| 3.20 | Circuit for stability analysis                                                                | 49 |

| 3.21 | Simplified circuit for stability analysis                                                     | 49 |

|      | Break loop for open loop gain analysis                                                        | 50 |

| 3.23 | Schematic with loop open                                                                      | 50 |

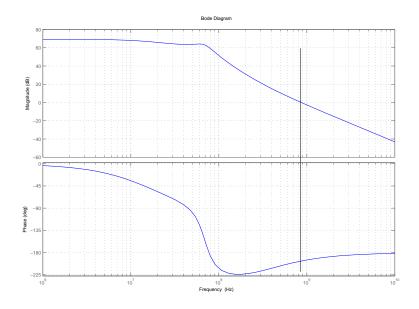

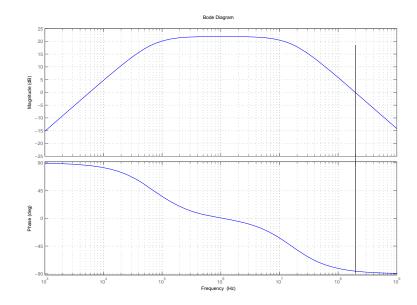

| 3.24 | Bode plot for the system open loop gain                                                       | 53 |

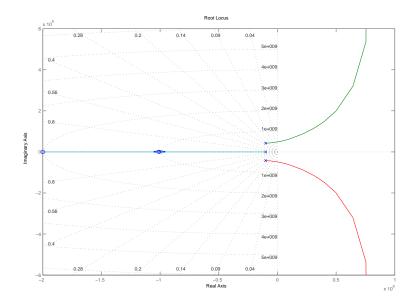

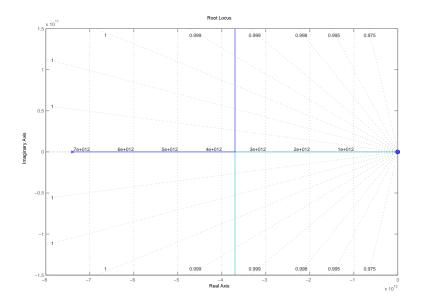

| 3.25 | Root locus for the system open loop gain                                  | 53 |

|------|---------------------------------------------------------------------------|----|

| 3.26 | Schematic with compensation network                                       | 54 |

| 3.27 | Bode plot for the compensated system open loop gain                       | 55 |

| 3.28 | Root locus for the compensated system open loop gain                      | 55 |

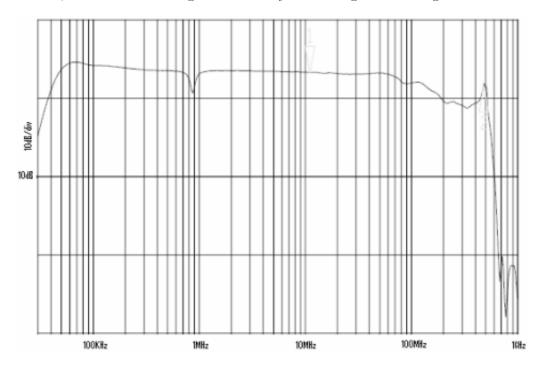

| 3.29 | $S_{21}$ parameter for the SCM with THS3202 and $R_{FB} = 700\Omega$      | 56 |

| 3.30 | $S_{21}$ parameter for the SCM with THS3202 and $R_{FB} = 300\Omega$      | 57 |

| 3.31 | $S_{21}$ parameter for the SCM with AD8009 and $R_{FB} = 220\Omega$       | 58 |

| 3.32 | Transimpedance gain for the current probe (second version)                | 58 |

| 3.33 | Input impedance for the SCM second version                                | 59 |

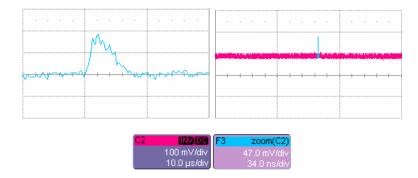

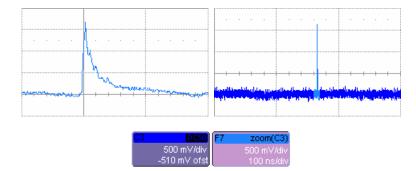

| 3.34 | Current peak measured with resistance (zoom on the left)                  | 59 |

| 3.35 | Current peak measured with the current probe (zoom on the left)           | 60 |

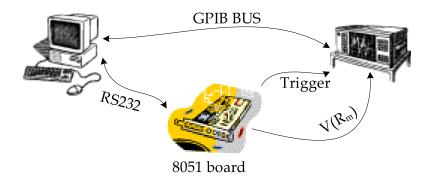

| 3.36 | Measurement setup                                                         | 61 |

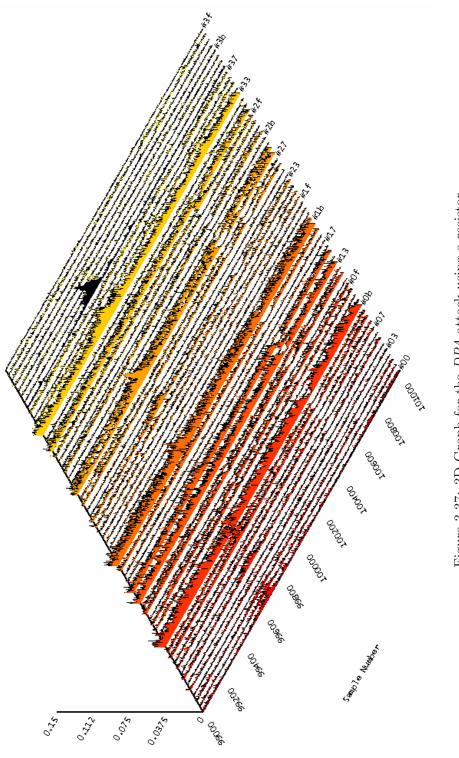

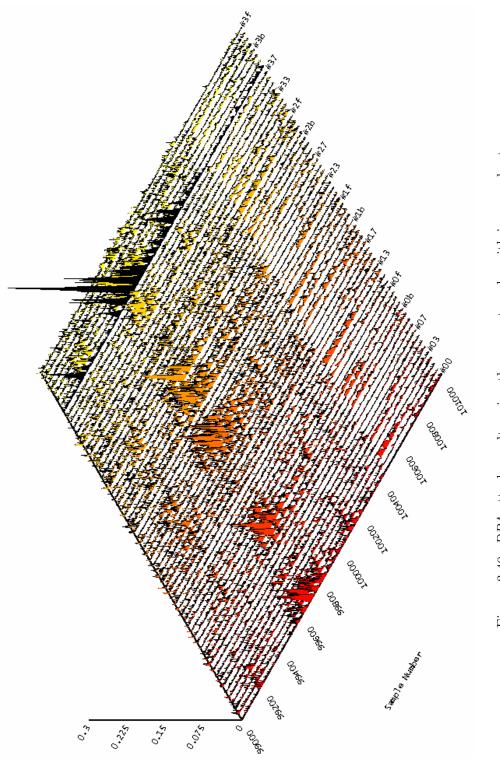

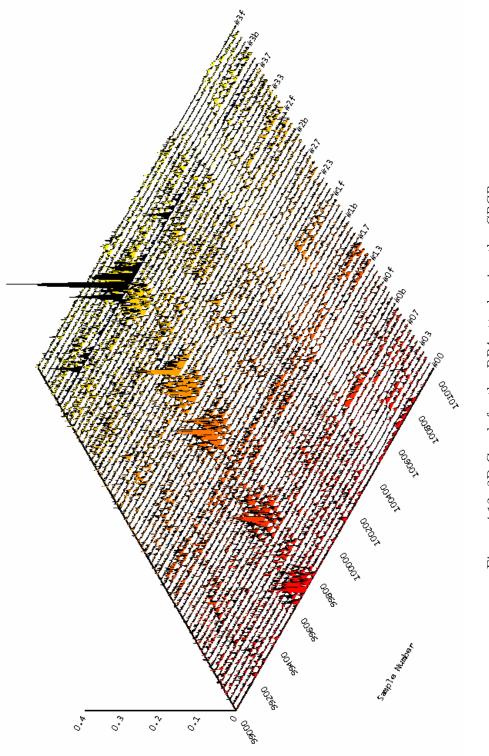

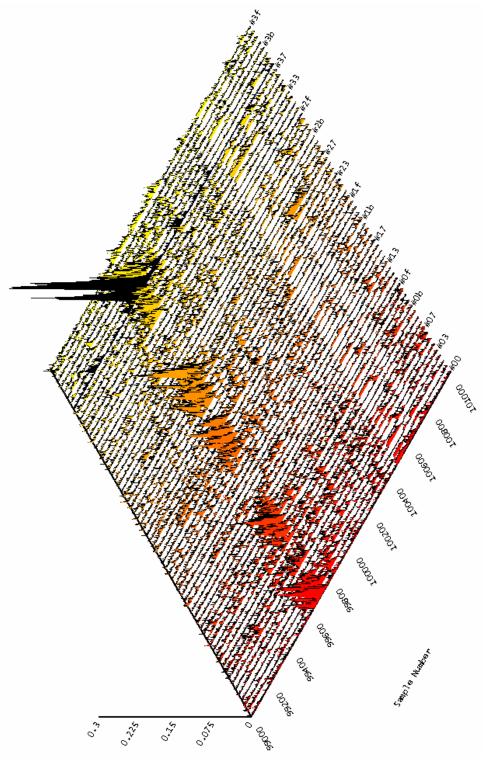

| 3.37 | 3D Graph for the DPA attack using a resistor                              | 62 |

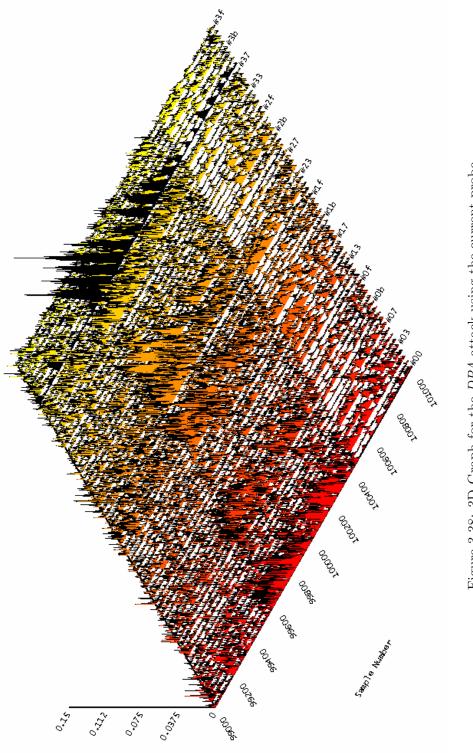

| 3.38 | 3D Graph for the <i>DPA</i> attack using the current probe                | 63 |

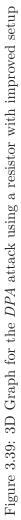

| 3.39 | 3D Graph for the $DPA$ attack using a resistor with improved setup .      | 64 |

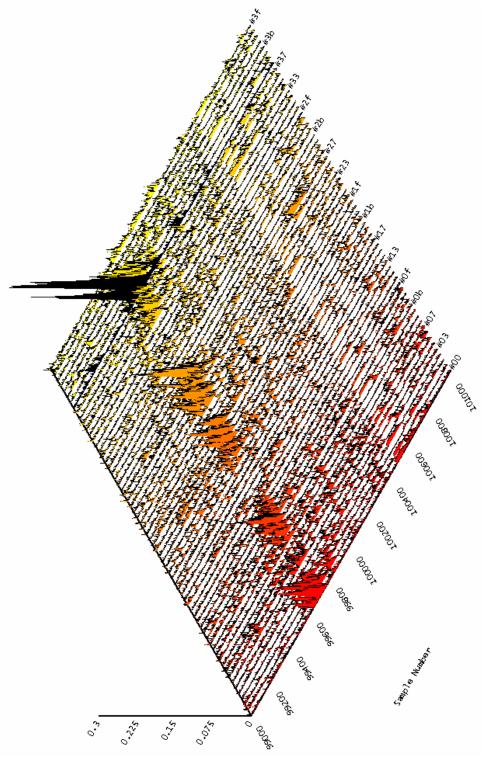

| 3.40 | $DP\!A$ attack results using the current probe with improved setup $~$ .  | 65 |

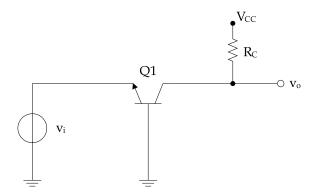

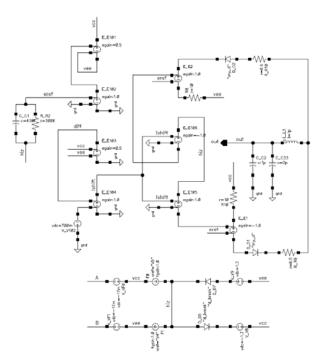

| 4.1  | Common Base Current Probe schematic                                       | 67 |

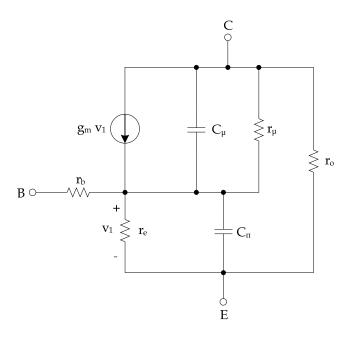

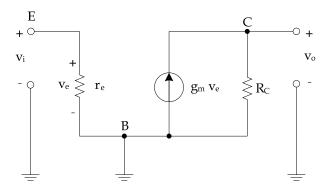

| 4.2  | Common base configuration                                                 | 67 |

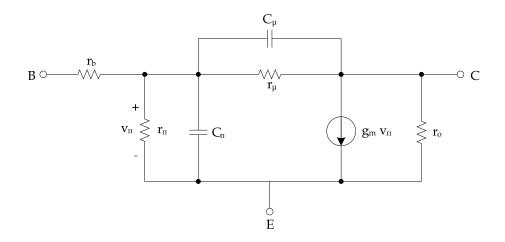

| 4.3  | Small signal equivalent circuit                                           | 68 |

| 4.4  | Equivalent circuit with two controlled generators                         | 68 |

| 4.5  | Generation of the emitter-current-controlled T model                      | 69 |

| 4.6  | Low frequency, small signal equivalent circuit                            | 69 |

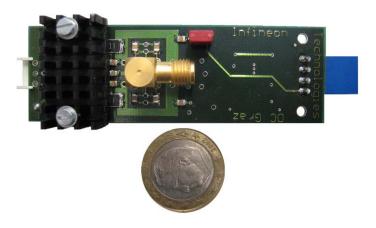

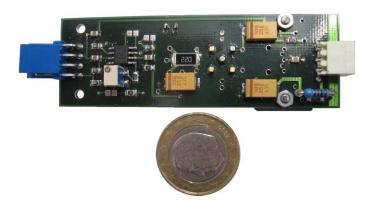

| 4.7  | Front view of the common base current probe                               | 73 |

| 4.8  | Back view of the common base current probe                                | 73 |

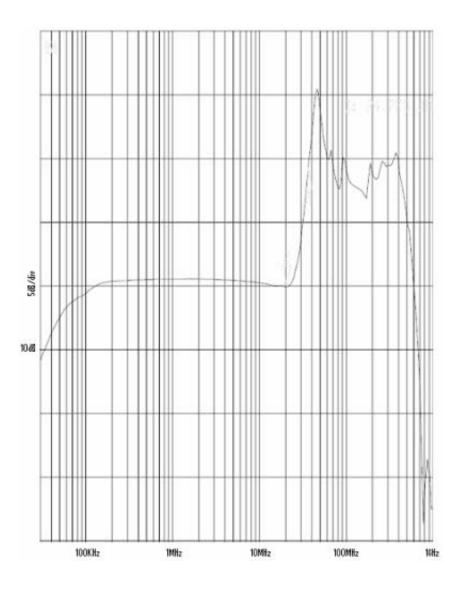

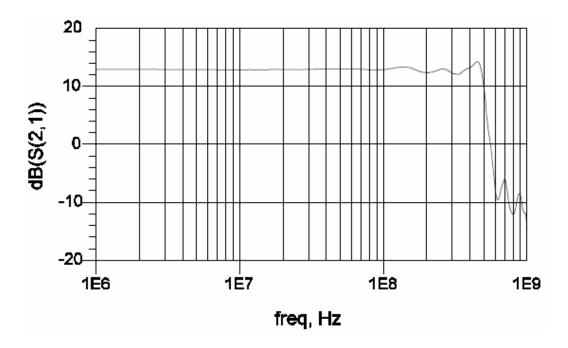

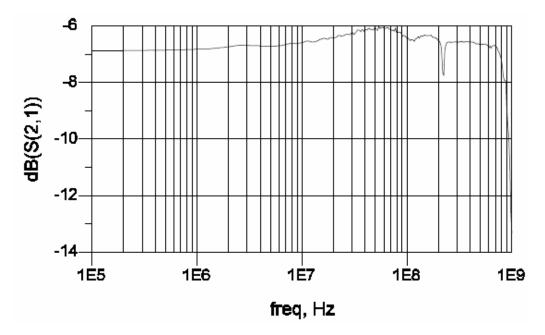

| 4.9  | $S_{21}$ parameter for the <i>CBCP</i>                                    | 74 |

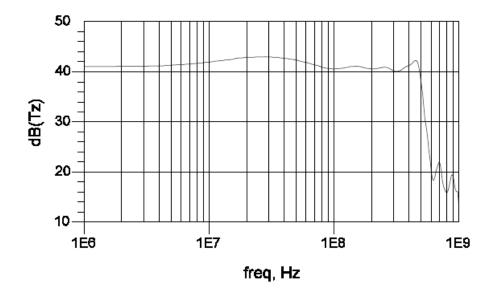

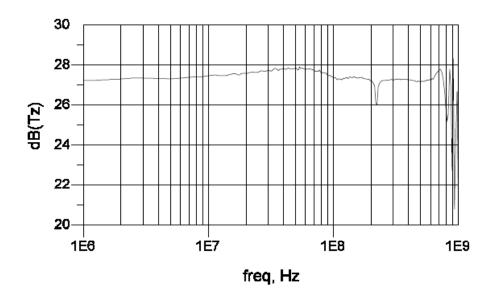

| 4.10 | Transimpedance characteristic for the <i>CBCP</i>                         | 75 |

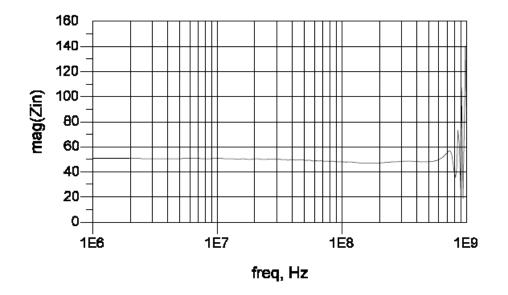

| 4.11 | Input impedance for the <i>CBCP</i>                                       | 75 |

| 4.12 | 3D Graph for the DPA attack using the CBCP                                | 76 |

| 4.13 | 3D Graph for the <i>DPA</i> attack using the resistor-based setup         | 78 |

| A -1 |                                                                           | 00 |

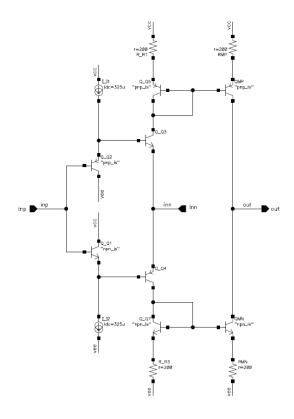

| A.1  | Internal structure of $THS3201$ model input stage                         | 82 |

|      | Internal structure of $THS3201$ model output stage $\ldots \ldots \ldots$ | 83 |

| A.3  | Simplified schematic for the <i>THS3201</i> input buffer                  | 85 |

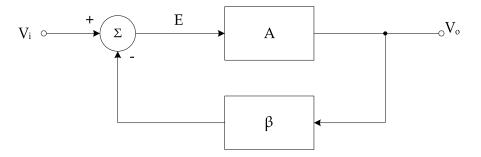

| B.1  | Feedback system block diagram                                             | 86 |

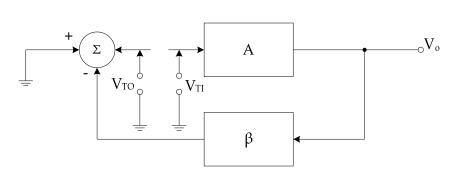

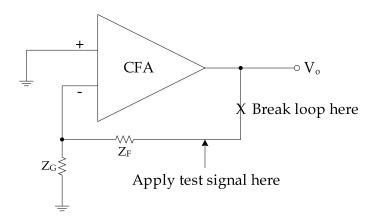

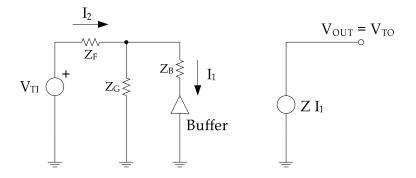

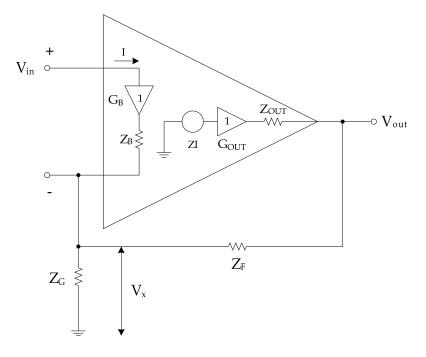

| B.2  | Block diagram for computing the loop gain                                 | 88 |

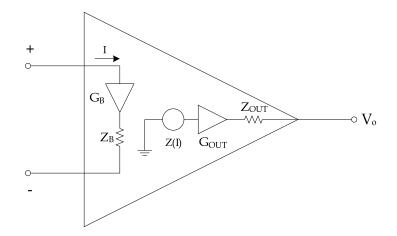

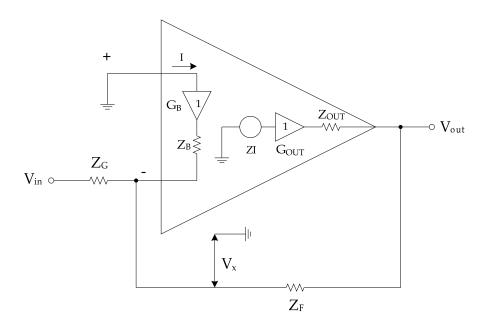

| B.3  | Current feedback amplifier model                                          | 89 |

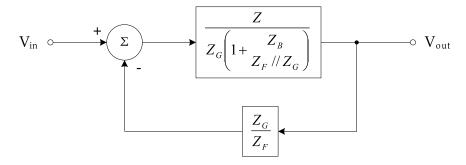

| B.4  | Block diagram for stability analysis                                      | 89 |

| B.5  | Internal circuit for stability analysis                                   | 89 |

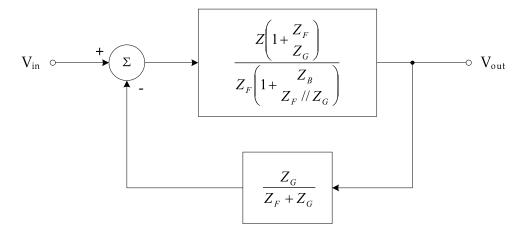

| B.6  | Non-inverting configuration circuit                                       | 90 |

| B.7  | Block diagram of the non-inverting CFA                                    | 91 |

| B.8  | Inverting circuit diagram                                                 | 92 |

| B.9  | Block diagram of the inverting CFA                                        | 92 |

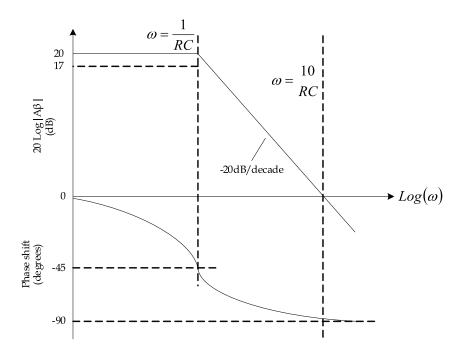

| B.10 | Sample Bode plot for a single pole circuit         |   | • | <br> |     |  |   | 93  |

|------|----------------------------------------------------|---|---|------|-----|--|---|-----|

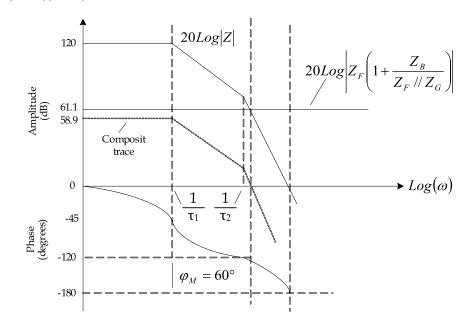

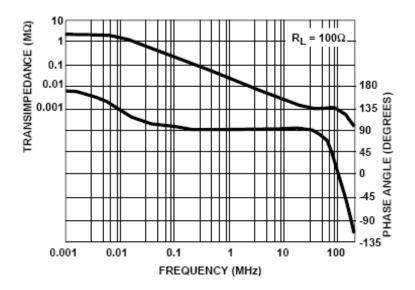

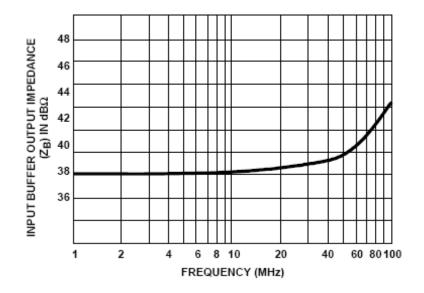

| B.11 | CFA transimpedance plot                            |   |   | <br> |     |  |   | 94  |

| B.12 | Transimpedance $Z$ vs frequency                    |   |   | <br> |     |  |   | 96  |

| B.13 | Input buffer output resistance vs frequency        | • | • |      | • • |  | • | 96  |

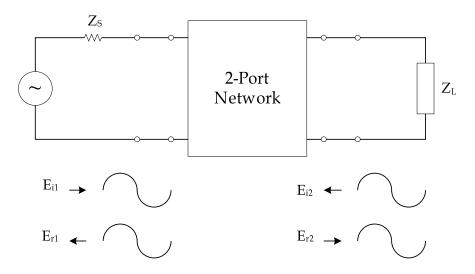

| C.1  | Transmission line with two-port network tampered . | • | • |      |     |  |   | 100 |

|      |                                                    |   |   |      |     |  |   |     |

# List of Tables

| 1.1 | Objectives associated with information security                                                                                 | 13 |

|-----|---------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1 | Main features of the SCM circuit                                                                                                | 32 |

| 4.1 | BLT70 limiting values                                                                                                           | 72 |

| 5.2 | Main features of the SCM - first versionMain features of the SCM - second versionMain features of the common base current probe | 80 |

| B.1 | Summary of <i>OPAMP</i> equations                                                                                               | 97 |

### Preface

Side channel attacks can reveal confidential data (i.e. cryptographic keys and user PIN's) exploiting the information leaked by the hardware implementation of cryptographic algorithms.

This thesis work is devoted to design an active current probe to implement power analysis attacks on crypto-processors. A short introduction on smart cards and cryptography is reported in Chapter 1. In the second chapter, different types of side channel attacks are discussed. In particular, power analysis attacks, simple and differential, are based on the fact that logic operations feature a power consumption profile dependent on the processed data: with simple statistical analyses of a sufficient number of power traces, the correlation between circuit switching activity and key material can be revealed.

In Chapter 3, an active current probe tested on a FPGA in a previous thesis work is shortly discussed, pointing out its main drawbacks. In particular, the maximum amplitude of the input current peaks is limited to about 7mA, which is not sufficient in some cases.

As a first step, some changes on this first probe have been implemented to improve its performance, by testing different components for both the transimpedance amplifier and the output voltage buffer. The main goal was to achieve a better gain-bandwidth product.

Even if these changes shown some improvement with respect to the initial design, they did not provide the expected advantages, when compared with a resistor-based measuring setup. Moreover, the stability was an issue and the introduction of an additional compensation network was necessary.

For these reasons, a different circuit based on a common base configuration was adopted (Chapter 4), designing a new probe which can measure current peaks close to 100mA, maximum allowed current consumption in a class A smart card<sup>1</sup>. Experiment results showed a substantial improvement with respect to the original design and a resistor-based measurement as well.

The main features of the three different active current probes evaluated in this work are summarized in Chapter 5, where the better performance of the common-base current probe are pointed out.

In appendix, a description of the Texas Instruments THS320X internal structure is reported and a short theory of current feedback amplifiers (*CFA*) is provided. Finally, the measurement of S-parameters is discussed.

I wish to thank **Alessandro Trifiletti**, **Raimondo Luzzi** and **Marco Bucci** for their valuable support.

I wish you a pleasant reading, Michele Marino

<sup>&</sup>lt;sup>1</sup>Smart cards can be divides in three class (A, B and C) based on their peak current consumptions.

# Chapter 1

# Smartcards & Cryptography

The proliferation of plastic cards started in the USA in the early 1950s. The first all-plastic payment card for general use was issued by the *Diners Club* in 1950. It was intended for an exclusive class of individual, and thus also served as a status symbol, allowing the holder to pay with his or her 'good name' instead of cash. The entry of *Visa* and *MasterCard* into the field led to a very rapid proliferation of 'plastic money' in the form of credit cards.

Today, credit cards allow travelers to shop without cash everywhere in the world. At first, the functions of these cards were quite simple. They served as data storage media that were secure against forgery and tampering. General information, such as the card issuer's name, was printed on the surface, while personal data elements, such as the cardholder's name and the card number, were embossed. In these first-generation cards, protection against forgery was provided by visual features, such as security printing and the signature panel. Consequently, the system's security depended quite fundamentally on the quality and conscientiousness of the persons responsible for accepting the cards. With the increasing proliferation of card use, these rather rudimentary features no longer proved sufficient, particularly since threats from organized criminals were growing apace. It became apparent that the security features for protection against fraud and manipulation, as well as the basic functions of the card, had to be expanded and improved.

The first improvement consisted of a magnetic stripe on the back of the card, which allowed digital data to be stored on the card in machine-readable form as a supplement to the visual information. This made it possible to minimize the use of paper receipts. This made it possible to finally achieve the long-standing objective of replacing paper-based transactions by electronic data processing. This required a different method to be used for user identification, which previously employed the user's signature. The method that has come into widespread general use involves a secret personal identification number (*PIN*) that is compared with a reference number. However, magnetic-stripe technology has a crucial weakness, which is that the data stored on the stripe can be read, deleted and rewritten at will by anyone with access to the necessary equipment. It is thus unsuitable for storing confidential data.

Most systems use online connections to the system's host computer for reasons of security, even though this generates significant costs for the necessary data transmissions. In order to reduce costs, it is necessary to find solutions that allow card transactions to be executed offline without endangering the security of the system. The development of the smart card, combined with the expansion of electronic data processing systems, has created completely new possibilities for devising such solutions.

Enormous progress in microelectronics in the 1970s made it possible to integrate data storage and processing logic on a single silicon chip measuring a few square millimeters. The great breakthrough was achieved in 1984, when the French *PTT* (*Postal and Telecommunications services agency*) successfully carried out a field trial with telephone cards. In this field trial, smart cards immediately proved to meet all expectations with regard to high reliability and protection against manipulation. A pilot project was conducted in Germany in 1984-85, using telephone cards based on several technologies. Magnetic-stripe cards, optical-storage (*holographic*) cards and smart cards were used in comparative tests. Smart cards proved to be the winners in this pilot study. In addition to a high degree of reliability and security against manipulation, smart card technology promised the greatest degree of flexibility for future applications.

Further developments followed the successful trials of telephone cards. Telephone cards incorporating chips are currently used in more than fifty countries. The integrated circuits used in telephone cards are relatively small, simple and inexpensive memory chips with specific security logic that allows the card balance to be reduced while protecting it against manipulation.

In 1988, the German Post Office acted as a pioneer in this area by introducing a modern microprocessor card using *EEPROM* technology as an authorization card for the analog mobile telephone network. The positive experience gained from using smart cards in the analog mobile telephone system was decisive for the introduction of smart cards into the digital *GSM* network.

Progress was significantly slower in the field of bank cards, in part due to their greater complexity compared with telephone cards. Modern hardware and software made it possible to implement complex, sophisticated mathematical algorithms that allowed previously unparalleled levels of security to be achieved. Moreover, this new technology was available to everyone, in contrast to the previous situation in which cryptography was a covert science in the private reserve of the military and secret services.

The smart card proved to be an ideal medium. It made a high level of security (based on *cryptography*) available to everyone, since it could safely store secret keys and execute cryptographic algorithms. In addition, smart cards are so small and easy to handle that they can be carried and used everywhere by everybody in everyday life. It was a natural idea to attempt to use these new security features for bank cards. However, the problems associated with making small payments securely but anonymously throughout the world via the public Internet have not yet been solved in a satisfactory manner. Smart cards could play a decisive role in providing an answer to these problems. Besides this, smart cards could plan an important role in introducing electronic signatures.

The predominant practitioners of the *cryptography* were those associated with the military, the diplomatic service and government in general. Cryptography was used as a tool to protect national secrets and strategies. The proliferation of computers and communications systems in the 1960s brought with it a demand from the private sector for means to protect information in digital form and to provide security services. Beginning with the work of Feistel at IBM in the early 1970s and culminating in 1977 with the adoption as a U.S. Federal Information Processing Standard for encrypting unclassified information, DES, the Data Encryption Standard, is the most well-known cryptographic mechanism in history. The most striking development in the history of cryptography came in 1976 when Diffie and Hellman published New Directions in Cryptography. This paper introduced the revolutionary concept of *public-key cryptography* and also provided a new and ingenious method for key exchange. In 1978 Rivest, Shamir, and Adleman discovered the first practical *public-key encryption* and signature scheme, now referred to as RSA. The RSA scheme is based on another hard mathematical problem, the intractability of factoring large integers.

One of the most significant contributions provided by public-key cryptography is the digital signature. In 1991 the first international standard for digital signatures (ISO/IEC 9796 - International Organization for Standardization / International Electrotechnical Commission) was adopted. It is based on the RSA publickey scheme. Regardless of who is involved, to one degree or another, all parties to a transaction must have confidence that certain objectives associated with information security have been met. Some of these objectives are listed in Table 1.1.

Often the objectives of information security cannot solely be achieved through mathematical algorithms and protocols alone, but require procedural techniques and abidance of laws to achieve the desired result.

Whereas information was typically stored and transmitted on paper, much of it now resides on magnetic media and is transmitted via telecommunications systems, some wireless. What has changed dramatically is the ability to copy and alter information.

What is needed then for a society where information is mostly stored and transmitted in electronic form is a means to ensure information security which is independent of the physical medium recording or conveying it and such that the objectives of information security rely solely on digital information itself. One of the fundamental tools used in information security is the signature. It is a building block for many other services such as non-repudiation, data origin authentication, identification, and witnessing, to mention a few. This signature is intended to be unique to the individual and serve as a means to identify, authorize, and validate. With electronic information the concept of a signature needs to be redressed; it cannot simply be

| Privacy or confidentiality | keeping information secret from              |

|----------------------------|----------------------------------------------|

|                            | all but those who are authorized to see it   |

| Data integrity             | ensuring information has not been            |

|                            | altered by unauthorized or unknown means     |

| Entity authentication      | corroboration of the identity of an entity   |

| or identification          | (e.g., a person, a computer terminal,        |

|                            | a credit card, etc.)                         |

| Message authentication     | corroborating the source                     |

|                            | of information; also known as data           |

|                            | origin authentication                        |

| Signature                  | a means to bind information to an entity     |

| Authorization              | conveyance, to another entity, of official   |

|                            | sanction to do or be something               |

| Validation                 | a means to provide timeliness of             |

|                            | authorization to use or manipulate           |

|                            | information or resources                     |

| Access control             | restricting access to resources              |

|                            | to privileged entities                       |

| Certification              | endorsement of information                   |

|                            | by a trusted entity                          |

| Time stamping              | recording the time of creation or            |

|                            | existence of information                     |

| Witnessing                 | verifying the creation or existence          |

|                            | of information by an entity                  |

|                            | other than the creator                       |

| Receipt                    | acknowledgement that information             |

|                            | has been received                            |

| Confirmation               | acknowledgement that services                |

|                            | have been provided                           |

| Ownership                  | a means to provide an entity                 |

|                            | with the legal right to use                  |

|                            | or transfer a resource to others             |

| Anonymity                  | concealing the identity of an entity         |

|                            | involved in some process                     |

| Non-repudiation            | preventing the denial of previous            |

|                            | commitments or actions                       |

| Revocation                 | retraction of certification or authorization |

Table 1.1: Objectives associated with information security

something unique to the signer and independent of the information signed.

There is, however, no guarantee that all of the information security objectives deemed necessary can be adequately met. The technical mean is provided through cryptography. Cryptography is the study of mathematical techniques related to aspects of information security such as confidentiality, data integrity, entity authentication, and data origin authentication. Of all the information security objectives listed in Table 1.1, the following four form a framework upon which the others will be derived:

- *Confidentiality* is a service used to keep the content of information from all but those authorized to have it. *Secrecy* is a term synonymous with confidentiality and privacy.

- *Data integrity* is a service which addresses the unauthorized alteration of data. To assure data integrity, one must have the ability to detect data manipulation by unauthorized parties.

- Authentication is a service related to identification. This function applies to both entities and information itself. Two parties entering into a communication should identify each other. Information delivered over a channel should be authenticated as to origin, date of origin, data content, time sent, etc.

- *Non-repudiation* is a service which prevents an entity from denying previous commitments or actions. When disputes arise due to an entity denying that certain actions were taken, a means to resolve the situation is necessary.

A fundamental goal of cryptography is to adequately address these four areas in both theory and practice. Cryptography is about the prevention and detection of cheating and other malicious activities.

# Chapter 2

# Attacking techniques

### 2.1 Physical Attacks on Smart Cards

The most obvious and direct attack on a smart card is a physical attack on the card itself. In the case of a stored-value card, this sort of attack may even be carried out by the owner of a card. Physical attacks attempt to reverse engineer the card and determine the secret key(s). Such attacks have been demonstrated in practice against commercial secure smart card chips, most notably by three groups of researchers: Dan Boneh, Richard DeMillo, and Richard Lipton of Bellcore; Ross Anderson of Cambridge and Marcus Kuhn of Purdue; and Paul Kocher and colleagues of Cryptography Research, Inc.

Tamper resistance is not absolute: an attacker with access to semiconductor test equipment can retrieve key material from a smart card controller by direct observation and manipulation of the chip's components. It is generally believed that, given sufficient investment, any chip-sized tamper resistant device can be penetrated in this way.

In [1] was pointed that "smart cards are broken routinely" and to the extent that their secure use requires tamper resistance, smart cards "should be treated with circumspection". The paper describes a number of smart card attacks, many of which can be carried out by amateur attackers with very limited resources. Attacks described include voltage manipulation, temperature manipulation, chip removal (for easier probing), UV (Ultra Violet) light attacks, and microprobing.

More sophisticated attacks requiring professional equipment and materials involve uncovering the layers of a chip by etching, discerning chip behavior by advanced infrared probing, and reverse-engineering chip logic. The somewhat gloomy conclusion is that, at best, chip designers can only impose costs and delays on attackers, never providing guaranteed security. Many businesses that rely on smart card security realize this and do all they can to manage the risks prudently. Users should do the same. Some caveats: the *Anderson* and *Kuhn* [1] work is somewhat dated and is based on attacks carried out in the lab against conventional *micro-controllers*, which are usually much simpler than today's smart cards. *Micro-controllers* provide a great deal of open access to potential attackers since they are meant to be interactively programmed. For example, micro-controllers often provide an interface for external memory; generally speaking, smart cards don't have this feature. Thus they provide less of a beachhead for attacks.

### 2.2 Fault attacks

In [3] was pointed out that an adversary who can introduce computational errors into a smart card can deduce the values of cryptographic keys hidden in the smart card. The surprising part is that an attacker can do this even without precisely controlling the nature of the errors or even the exact timing of the errors. By comparing the result of an erroneous encryption with the result of a correct encryption of the same data, the attacker can learn something about the correct encryption key. By doing enough of these comparisons, the attacker can learn enough information to deduce the entire encryption key. Boneh et al. classified the faults into three categories. The first type are transient faults which can occur randomly causing a faulty computation to be executed. The second type are latent faults, which are hardware or software bugs that are difficult to locate. The third type are induced faults for which physical access to the hardware is necessary. These are the most interesting because of the active role of the attacker. For example, optical fault induction attacks, as introduced by Scorabogatov and Anderson [4], use a flashgun targeting a transistor to change the state of a memory cell in a microcontroller.

Fault attacks can be considered as the most dangerous implementation attacks as countermeasures usually include complex techniques which are not easy to implement on constrained environment such as smart cards.

In [5], this attack was generalized a technique called "Differential Fault Analysis", which works against a wide range of cryptographic algorithms. The upshot of all this is that unless a smart card cryptography mechanism is very carefully designed, any secret keys stored inside the card might be extracted by a determined attacker.

### 2.3 Side-channel attacks

Cryptographic algorithms are building blocks of many security protocols and can be implemented both in software and hardware. Software solutions are cheaper and more flexible, while hardware implementations provide higher speed and intrinsic security. A trade-off in cost and speed can be achieved by hardware-software codesign.

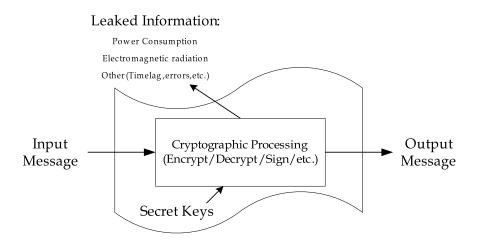

Namely, attacks on cryptographic algorithms are usually divided into mathematical and implementation attacks. The latter are based on weaknesses in the implementation and can be passive or active. Passive attacks are also called sidechannel attacks as they benefit from side channel information, which is collected by measuring some physical quantity. More precisely, while secret data are being processed they can be deduced by observing execution time, power consumption, electromagnetic radiation, etc. The second class of implementation attacks, i.e. the active attacks, is more invasive as they are based on the introduction of faults, which result in erroneous calculations leading to the exposure of the secret key. The usual cause of these faults can be sudden changes, i.e. glitches, in various parameters such as power supply, clock, temperature, etc. An attacker could also use a light flash with equipment such as a camera flash or a laser in order to induce a fault. Figure 2.1 is a conceptual diagram of side-channel attacks.

Figure 2.1: Side-channel attacks diagram

#### 2.3.1 Timing attacks

Timing analysis attacks are based on the fact that algorithms with a nonconstant execution time can leak secret information. A non-constant execution time can be caused by conditional branches in the algorithm, various optimization techniques, cache hits, etc. Unlike power attacks, the use of these attacks is not restricted to cryptographic tokens. Timing attacks can also be applied to network based cryptosystems [2] and to other applications whenever the attacker can get hold of timing information. The obvious way to prevent timing attacks is to implement cryptographic algorithms with a constant execution time. Almost all modern implementations are resistant against timing attacks, which makes a timing-only attack impossible. However, the threat remains in combining timing information with other side-channels. For example, timing information can be used by an attacker in order to locate specific parts of the algorithm.

#### 2.3.2 Power Analysis Foundations

In 1998, researchers at Cryptography Research Inc., led by Paul Kocher, publicly announced a new set of attacks against smart cards called Power Analysis (PA)

[6]. The *PA* can be carried out successfully against most smart cards currently in production.

The PA is a simple attack that relies on statistical inferences drawn on power consumption data measured during smart card computation. The equipment required to perform the PA is simple: a modified smart card reader and some off-the-shelf PCs. The algorithm itself is quite complex, but details have been widely published.

Chips inside a smart card use different amounts of power to perform different operations. By hooking a card up to an oscilloscope, a pattern of power consumption can be measured. Particular computations create particular patterns of spikes in power consumption. Careful analysis of the peaks in a power consumption pattern can lead to the discovery of information about secret keys used during cryptographic computations. Sometimes the analysis is straightforward enough that a single transaction provides sufficient data to steal a key. More often, thousands of transactions are required. The types of sensitive information that can leak include *PINs* and private cryptographic keys.

Possible solutions include masking power consumption with digital noise or throwing random calculations into the mix. Another potential solution is randomizing the order of card computations so that in the end, the same computation is performed using different patterns of primitives. All of these potential technological solutions are ways to mask the patterns in the power consumption of the card.

DPA is actually a variation on an earlier attack discovered by Kocher. The earlier attack exploited the fact that some operations require different amounts of time to finish, depending on which values they are computing. In the same way that DPA allows an attacker to piece together key information based on variations in power consumption, Kocher's timing attack allows an attacker to piece together a key based on variations in the amount of computing time required to encrypt various values.

One thing to note is that legitimate users of smart cards don't have to worry too much about *DPA* or timing attacks, because the attack requires physical access to the card itself. Unless you lose your card or insert it directly into an attacker's machine, there is not much threat that your card itself will be cracked. The main risk that *DPA* presents is to companies that must concern themselves with widespread fraud of the sort carried out by organized crime.

The best approach is to assume information will leak from a smart card and design systems in such a way that they remain secure even in the face of leaking information. An approach of this sort may preclude smart card systems designed to do all processing offline without a centralized clearinghouse. Since increasingly confidential data are being exchanged on electronic way an ever greater importance is attached to the protection of the data. Where cryptosystems are being used in real applications not only mathematical attacks have to be taken into account. Hard and software implementations themselves present a vast field of attacks. *Side-Channel-Attacks* exploit information that leaks from a cryptographic device. Especially one of these new attacks has attracted much attention since it has been announced. This

method is called *Differential Power Analysis (DPA)* and was presented in 1998 by *Cryptography Research Inc.*. *DPA* uses the information that naturally leaks from a cryptographic hardware device, namely the power consumption. A less powerful variant, the *Simple Power Analysis (SPA)* was also announced by *Cryptography Research Inc.*. What does a *DPA* attack require? First, an attacker must be able to precisely measure the power consumption. Second, the attacker needs to know what algorithm is computed, and third an attacker needs the plain or ciphertexts. The strategy of the attacker is to make a lot of measurements, and then divide them with the aid of some selection function into two or more different sets. Then, statistical methods are used to verify the selection function. If and only if the selection function was right, one can see noticeable peaks in the statistics.

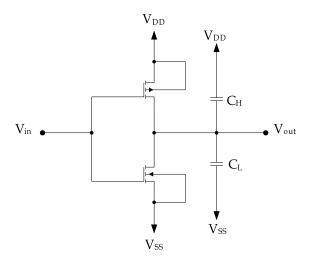

Almost every digital circuit built today is based on *Complementary Metal Oxide* Semiconductor (CMOS) technology. Therefore it is necessary to understand the power consumption characteristics of this technology. If a CMOS gate changes its state, this change can be measured at the  $V_{DD}$  ( $V_{SS}$ ) pin. The more circuits change their state, the more power is dissipated. In a synchronous design, gates are  $clocked^{1}$ which means that all gates change their state at the same time. Power dissipated by the circuit can be monitored by using a small resistor  $R_m$  in series between  $V_{DD}$ , (or  $V_{SS}$ ) and the true source (or ground). The two most essential parts of the power consumption during a change of a state are the dynamic charge resp. discharge (appr. 85%) and the dynamic short circuit current (appr. 15%). This is sketched on the example of an inverter (see Figure 2.2). The output of each gate has a capacitive load, consisting of the parasitic capacity of the connected wires and gates of the following stages. An input transition results in an output transition, which discharges or charges this parasitic capacity, causing a current flow to  $V_{DD}$  (or  $V_{SS}$ ). This current is the dynamic charge resp. discharge current. By measuring current flow on  $V_{DD}$  we can detect whether the output changed from 0 to 1 or not.

In differential CMOS logic, every output appears also in its inverted form, which means a transition always causes charge and discharge on the output and inverted output. By measuring current on  $V_{DD}$  or  $V_{SS}$  one can't distinguish high and low transitions, but it is possible to detect whether a transition occurred or not. Logic with precharge characteristic always charges the output capacity during a precharge cycle and discharges it during the evaluation cycle, in case that the output value differs from the precharge value. By observing current flow, one can detect changes of the output node. Precharge logic has much higher power consumption than differential or standard CMOS logic, because dynamic charge current appears also in situations where the output value doesn't toggle.

$<sup>^{1}</sup>$ In electronics and synchronous digital circuits, such as most computers, a *clock signal* is a signal used to coordinate the actions of two or more circuits.

Figure 2.2: CMOS Inverter

#### 2.3.3 Simple Power Analysis

Most modern cryptographic devices are implemented using semiconductor logic gates, which are constructed out of transistors. Electrons show across the silicon substrate when charge is applied to (or removed from) a transistor's gate, consuming power and producing electromagnetic radiation. To measure a circuit's power consumption, a small (e.g.,  $50 \ \Omega$ ) resistor is inserted in series with the power or ground input. The voltage difference across the resistor divided by the resistance yields the current. Simple Power Analysis (SPA) is a technique that involves directly interpreting power consumption measurements collected during cryptographic operations. SPA can yield information about a device's operation as well as key material.

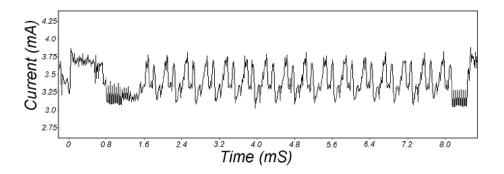

Figure 2.3: SPA trace from a typical smart card during a DES operation [6] A trace refers to a set of power consumption measurements taken across a cryp-

tographic operation. Figure 2.3 shows an SPA trace from a typical smart card as it performs a DES operation. Note that the 16 DES rounds are clearly visible.

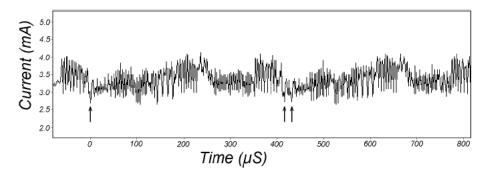

Figure 2.4: Detailed view of SPA trace [6]

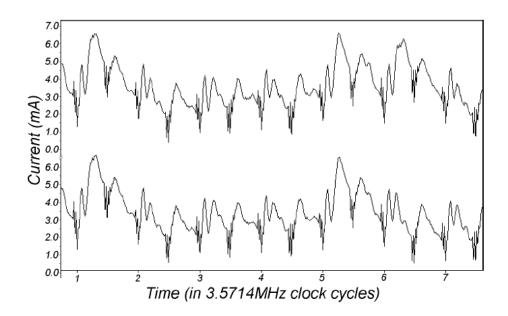

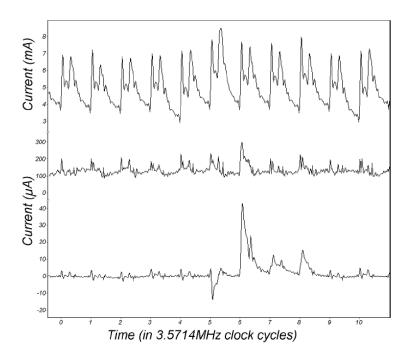

Figure 2.4 is a more detailed view of the same trace showing the second and third rounds of a *DES* encryption operation. Many details of the DES operation are now visible. For example, the 28-bit DES key registers C and D are rotated once in round 2 (*left arrow*) and twice in round 3 (*right arrows*). Figure 2.5 shows even higher resolution views of the trace showing power consumption through two regions, each of seven clock cycles at 3.5714 MHz.

The upper trace in Figure 2.5 shows the execution path through an SPA feature where a jump instruction is performed, and the lower trace shows a case where the jump is not taken. The point of divergence is at clock cycle 6 and is clearly visible.

Because *SPA* can reveal the sequence of instructions executed, it can be used to break cryptographic implementations in which the execution path depends on the data being processed.

#### 2.3.4 Differential power analysis

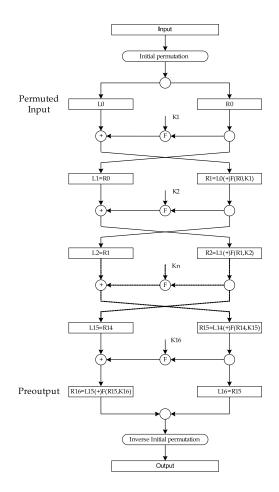

The *DES* (*Data Encryption Standard*) was invented in 1970 by *IBM*. It is an algorithm that takes a fixed-length string of plaintext bits and transforms it through a series of complicated operations into another ciphertext bitstring of the same length. In the case of *DES*, the block size is 64 bits. Before the main rounds, the block is divided into two 32-bit halves and processed alternately. It has a *Feistel-Structure* and consists of 16 rounds:

$$L_i = R_{i-1}$$

$$R_i = L_{i-1} \oplus f(R_{i-1}, K_i)$$

where  $f(R_{i-1}, K_i) = P(S(E(R_{i-1} \oplus K_i)))$

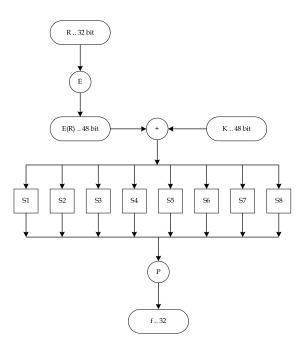

The *F*-function, depicted in Figure 2.7, operates on half a block (32 bits) at a time and consists of four stages:

Figure 2.5: Detailed view of SPA trace [6]

Figure 2.6: DES Algorithm

- Expansion the 32-bit half-block is expanded to 48 bits using the expansion permutation, denoted E in the diagram, by duplicating some of the bits.

- *Key mixing* the result is combined with a *subkey* using an *XOR* operation. Sixteen *48-bit* subkeys one for each round are derived from the main key.

- Substitution after mixing in the subkey, the block is divided into eight 6-bit pieces before processing by the S-boxes, or Substitution boxes. Each of the eight S-boxes replaces its six input bits with four output bits according to a non-linear transformation, provided in the form of a lookup table. The S-boxes provide the core of the security of DES without them, the cipher would be linear, and trivially breakable.

- *Permutation* finally, the 32 outputs from the *S*-boxes are rearranged according to a fixed permutation, the *P*-box.

As stated before, in each of the 16 rounds, the DES encryption algorithm performs eight *S*-box lookup operations. The 8 *S*-boxes each take as input six key bits exclusive-ORed with six bits of the *R* register and produce four output bits. The 32 S-output bits are reordered and exclusive-ORed onto *L*. The halves *L* and *R* are then exchanged. The DPA selection function D(C;b;Ks) is defined as computing the value of bit  $0 \le b < 32$  of the DES intermediate *L* at the beginning of the 16th round for ciphertext *C*, where the 6 key bits entering the *S*-box corresponding to bit *b* are represented by  $0 \le Ks < 2^6$ .

To implement the *DPA* attack, an attacker first observes m encryption operations and captures power traces  $T_{1...m}[1...k]$  containing k samples each. In addition, the attacker records the ciphertexts  $C_{1...m}$ . No knowledge of the plaintext is required. *DPA* analysis uses power consumption measurements to determine whether a key block guess Ks is correct. The attacker computes a k-sample differential trace  $\Delta_D[1...k]$  by finding the difference between the average of the traces for which D(C;b;Ks) is one and the average of the traces for which D(C;b;Ks) is zero.

Thus  $\Delta_D[j]$  is the average over  $C_{1...m}$  of the effect due to the value represented by the selection function D on the power consumption measurements at point j. If Ksis incorrect, the bit computed using D will differ from the actual target bit for about half of the ciphertexts  $C_i$ . The selection function D(Ci;b;Ks) is thus effectively uncorrelated to what was actually computed by the target device. If a random function is used to divide a set into two subsets, the difference in the averages of the subsets should approach zero as the subset sizes approach infinity. If Ks is correct, however, the computed value for D(Ci;b;Ks) will equal the actual value of target bit b with probability 1. The selection function is thus correlated to the value of the bit manipulated in the 16th round. As a result, the  $\Delta_D[j]$  approaches the effect of the target bit on the power consumption as  $m \to \infty$ . Other data values, measurement errors, etc. that are not correlated to D approach zero. Because power consumption is correlated to data bit values, the plot of  $\Delta_D$  will be at with spikes in regions where D is correlated to the values being processed.

Figure 2.7: Data Encryption Standard (F-function)

The correct value of Ks can thus be identified from the spikes in its differential trace. Four values of b correspond to each S-box, providing confirmation of key block guesses. Finding all eight Ks yields the entire 48-bit round subkey. The remaining 8 key bits can be found easily using exhaustive search or by analyzing one additional round. DPA can use known plaintext or known ciphertext and can find encryption or decryption keys.

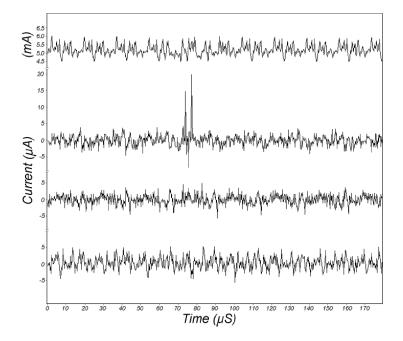

Figure 2.8 shows four traces prepared using known plaintexts entering a DES encryption function on another smart card. On top is the reference power trace showing the average power consumption during DES operations. Below are three differential traces, where the first was produced using a correct guess for Ks. The lower two traces were produced using incorrect values for Ks.

Figure 2.8: DPA traces for a DES encryption function [6]

Figure 2.9 shows the average effect of a single bit on detailed power consumption measurements. On top is a reference power consumption trace. The center trace shows the standard deviation in the power consumption measurements. Finally, the lower trace shows a differential trace prepared with  $m = 10^4$ . Note that regions that are not correlated to the bit are more than an order of magnitude closer to zero, indicating that little noise or error remains.

The size of the *DPA* characteristic is about  $40\mu A$ , which is several times less than the standard deviation observed at that point. The rise in the standard deviation at clock cycle 6 coinciding with a strong characteristic indicates that the operand value has a significant effect on the instruction power consumption and that there

Figure 2.9: Average effect of a single bit on DPA attack [6]

is considerable variation in the operand values being manipulated.

Several sources introduce noise into *DPA* measurements, including electromagnetic radiation and thermal noise. Quantization errors due to mismatching of device clocks and sample clocks can cause additional errors. Finally, uncorrected temporal misalignment of traces can introduce a large amount of noise into measurements. Several improvements can be applied to the data collection and *DPA* analysis processes to reduce the number of samples required or to circumvent countermeasures.

### 2.4 Countermeasures

Techniques for preventing simple power analysis are generally fairly simple to implement. Avoiding procedures that use secret intermediates or keys for conditional branching operations will mask many *SPA* characteristics. In cases such as algorithms that inherently assume branching, this can require creative coding and incur a serious performance penalty. Also, the microcode in some microprocessors cause large operand-dependent power consumption features.

In the recent years, a wide spectrum of countermeasures against differential power analysis *DPA* have been proposed in the technical literature. In a classification which takes into account the involved abstraction level during the design flow, three classes can be defined: system-level, gate-level and transistor-level countermeasures.

System-level techniques include adding noise to the device power consumption [7], duplicating logics with complementary operations [8], active supply current filtering with power consumption compensation [9], passive filtering, battery on chip and detachable power supply [10]. Notice that some of the mentioned countermeasures have a pure theoretical interest since, with the current state of the art, their employment to design tamper resistant cryptographic devices (e.g. chipcard microcontrollers) is limited by technological and cost constraints. As gate-level countermeasures, techniques that can be implemented using logic gates available in a standard-cell library are intended, e.g. random masking [11], random pre-charging [12], state transitions and Hamming weight balancing, random delay insertion [13]. Random masking is the most studied but, as it has been recently proved [14],[15], implementations in an automatic synthesis flow starting from a HDL description, can be still attacked exploiting glitches generated in the combinatorial networks when the random masks are applied.

Finally, the transistor-level approach is based on the adoption of a logic style whose power consumption is constant or independent of the processed data. In a dual-rail pre-charge (DRP) logic style (e.g. SABL [16], WDDL [17], Dual-Spacer DRP [18]), signals are encoded as two complementary wires and power consumption is constant under the hypothesis that the differential outputs of each gate drive the same capacitive load. Dual-rail pre-charge logics are not affected by glitches but building two balanced wires requires a full-custom approach thus increasing design and maintenance costs.

Recently, semi-custom design flows with support differential logic families have been proposed in the technical literature. An approach based on a technique for the automatic routing of balanced complementary lines is reported in [19]. Even if an automatic place and route could sensibly reduce design time and increase the portability, the proposed balanced routing technique does not take into account the dependence of the capacitive load on a line on the logic state of the adjacent wires and, furthermore, introduces additional constraints for the routing tool thus limiting its efficiency and, likely, causing an area overhead especially if only few metal layers are available for the inter-cell routing (as it is the case in a chipcard where the top layers are reserved for shielding). Moreover, in a modern deep submicron technology, intra-chip process gradients cannot be neglected and they are the limiting factor for the load matching accuracy.

A second approach proposed in [20] is based on a masked dual-rail pre-charge logic style (MDPL) where, due to the random masking at the gate level, power consumption is randomized. Moreover, since MDPL is a dual-rail pre-charge logic, glitches are avoided but, at the same time, the complementary wires do not need to be balanced thus removing the main drawback of the dual-rail circuits. On the other hand, the authors report in [21] a significant penalty in terms of area and, above all, power consumption with respect to a CMOS implementation. In [22] is proposed a further approach to the design of a dual-rail pre-charge logic family which is insensitive to unbalanced load conditions thus allowing adopting a semi-custom

design flow (automatic place & route) without additional constraints on the routing of the complementary wires.

The new concept is based on a three phase operation where an additional discharge phase is performed after the pre-charge/evaluation steps typical of any dynamic logic style. Although the concept is general, it can be implemented as an improvement of the SABL logic with a limited increase in circuit complexity.

## Chapter 3

# Supply and Current Measurement Probe

In this chapter, the design of the supply and current measurement probe (SCM) is described. Starting from a first version designed in a previous work [23], an enhanced circuit has been implemented and tested in a DPA attack.

### 3.1 First version: SCM

The starting point for a power analysis attack is the measurement of the instantaneous current consumption of the device under attack. In this work, an active probe for current measurement has been designed to be used to attack the implementation of encryption algorithms on a chip card.

The designed current probe can supply, and at the same time, measure the current consumption of the chip card. This technique shows several advantages with respect to a measurement with a resistance in series to the supply pin. Figure 3.1 shows the standard setup for a resistor-based measurement.

Figure 3.1: Current measurement with a resistor-based setup

The main drawbacks of this simple setup are the followings:

• The parasitic capacitance seen by the resistor introduces a time constant in the circuit that limits the measurement bandwidth. This effect can be neglected if the resistance R has a very small value.

- On the other side, the resistance provides the signal amplification and therefore a trade-off between signal bandwidth and amplification is necessary. A too low value for R can produce too noisy power consumption traces.

- Furthermore, the resistance causes a voltage drop, i.e. an insertion error, and the chip under measurement is supplied with:

$$V_{DD}^* = V_{DD} - R \cdot I(t)$$

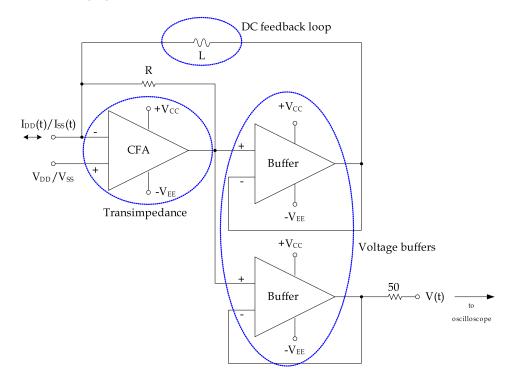

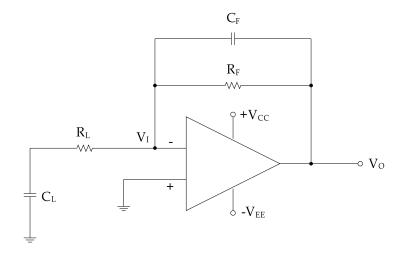

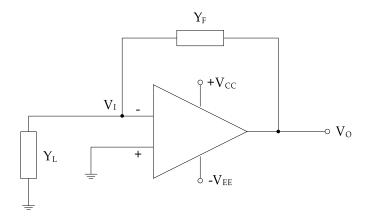

The active current probe is designed to overcome the limitations of a resistorbased setup. The main features of the SCM are a low input impedance, high transimpedance gain and, at the same time, it can supply the chip under test. Figure 3.2 shows the schematic of a first version of the circuit which was presented in a previous work [23].

Figure 3.2: SCM general circuit

The main block is a transimpedance amplifier (TZA), which drives two voltage buffers, whose reference input is connected to a power supply, either  $V_{DD}$  or  $V_{SS}$ . The voltage read on the output resistance, due to the voltage partition on the 50 $\Omega$ resistance, is:

$$V(t) = -\frac{R}{2} \cdot I_{DD}(t).$$

The gain is fixed by the feedback resistance that determines also the circuit stability. The value of the feedback resistance fixes the dynamic of the probe output as well.

Since the supply voltage for the circuit is  $\pm 5V$  and the value of  $R_F$  is fixed to 560 $\Omega$ , the maximum current spike which can be measured with this probe is about 7mA. This is quite a low value considering that a chip card is allowed to show current consumption spikes up to 100mA.

This version of the current probe has been used to supply and measure the current consumption of an Altera FPGA<sup>1</sup> MAX3000A with a 3.3V supply voltage. The buffers and the TZA are implemented with the AD8009 from Analog Device. This IC (Integrated Circuit) features a 1GHz maximum gain-bandwidth product and a  $5500V/\mu s$  slew rate.

The device under test is supplied by the probe throughout the upper buffer and the DC feedback loop closed by the inductance L. Therefore the probe can supply the measured device with a steady voltage  $V_{DD}$  or  $V_{SS}$ . The measurement signal is derived from the lower buffer, to decouple the TZA from the load shown by the measurement instrument.

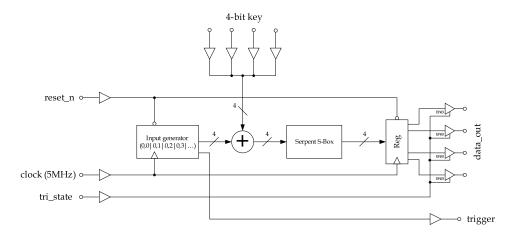

As a case study, the circuit shown in Figure 3.3 has been tested. It is a part of the *Serpent encryption algorithm* [24] and includes a 4 bit SBOX with the related output register, a XOR with a 4 bit key and a state machine that generates, in 256 clock transitions, a complete transition sequence on the 4 bit input data. The circuit has been synthesized on the FPGA MAX3000A starting from a *VHDL* description.

Figure 3.3: Serpent algorithmic

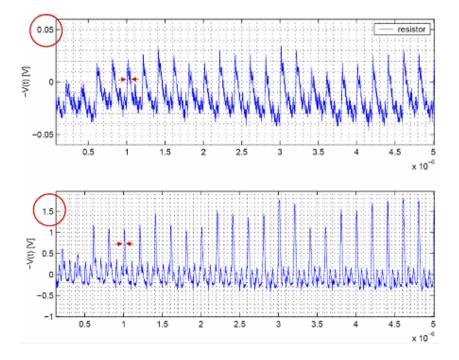

The same measurement has been performed using a resistor-based setup. Figure 3.4 shows that the resistor-base measurement produces spike output of about 50mV.

<sup>&</sup>lt;sup>1</sup>A **Field Programmable Gate Array** or **FPGA** is a semiconductor device containing programmable logic components and programmable interconnections.

This value is about 40 time lower than the value obtained using the SCM.

Figure 3.4: Comparison of experimental results obtained with both methods

| parameter         | Value           | Description               |  |  |  |  |

|-------------------|-----------------|---------------------------|--|--|--|--|

| R                 | $500\Omega$     | Transimpedance resistance |  |  |  |  |

| TZA               | 250V/A          | Transimpedance gain       |  |  |  |  |

| BW                | > 300 MHz       | Bandwidth                 |  |  |  |  |

| $f_L$             | $\approx 1 MHz$ | Low frequency cut         |  |  |  |  |

| $+V_{CC}/-V_{EE}$ | +5/-5V          | SCM supply voltage        |  |  |  |  |

| $+V_{CC}/-V_{SS}$ | +3.3/0V         | FPGA supply voltage       |  |  |  |  |

The main features of the SCM circuit are summarized in Table 3.1..

Table 3.1: Main features of the SCM circuit

### 3.2 Second version: current probe

The next step consisted in the replacement of the AD8009 component with a THS3202 amplifier from Texas Instruments, due to the better performance of this components. The THS3202 features a gain-bandwidth product of 2GHz and a slew rate of  $9000V/\mu s$ . The circuit has been simulated in SPECTRE and showed a very

poor stability and high sensitivity to component parametric variations. The circuit was optimized by adding an RC input network, as shown in Figure 3.5. The transfer function was analyzed in MATLAB: the additional RC network introduces a pole at the same frequency of the dominant pole due to the TZA and one zero in the negative half plane.

This poles/zero placement can stabilize the circuit with a careful choice of the external components. However, the THS3202 consists of two TZA amplifiers in the same chip and the isolation of the second TZA without performance and stability loss was an issue.

For these reasons, the current probe was modified by substituting the THS3202 with a THS3201 from Texas Instruments (gain-bandwidth product of 1.8GHz and a slew rate of  $10500V/\mu s$ ), and removing the DC feedback loop and the related voltage buffer. The new circuit is shown in Figure 3.5, where we can see the presence of decoupling capacitors on both THS3201 inputs and in inductance to shunt the DC component of the current consumption under measurement. Since the measurement circuit is now decoupled from the circuit under test, it does not supply the device as before, but it can only measure its current consumption. This configuration can measure up to 25mA current spikes and it is more stable than the version with THS3202.

Figure 3.5: SCM Schematic of the second version

Another reason for the DC decoupling was also to isolate the different ground planes in the board from the ground of the chip under test, thus avoiding noises and spurious oscillations. Figure 3.6 show an AC simulation of SCM second version circuit.

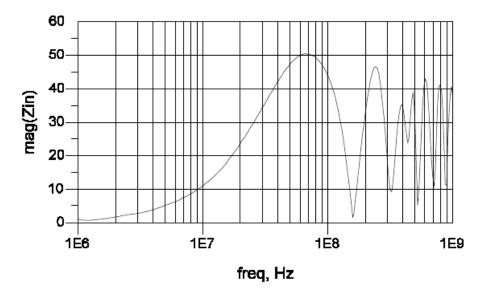

The high frequency cut is placed at about 550MHz, while the low frequency cut is at about 4MHz. The following Figures show the impedance measured looking into the circuit input (measurement input): it results that the input impedance is under  $5\Omega$  in a frequency range between 800KHz and 600MHz. This is a value low enough

Figure 3.6: AC response of the second version

to avoid sensitive effects on the chip card during the current measurement.

### **3.3** Transfer function calculation

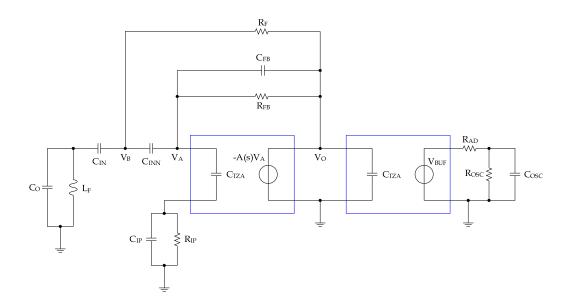

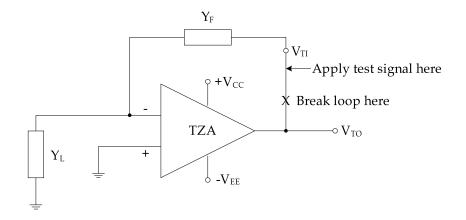

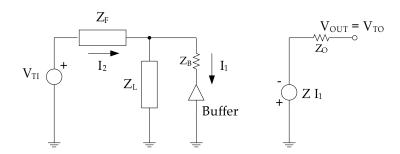

Figure 3.9 shows the circuit used for the transfer function calculation where the buffer and transimpedance amplifier are replaced with the respective functional models.

The circuit can be simplified by removing capacitors  $C_{IN}$  and  $C_{IP}$  since these are very large with respect to the other capacitors and their reactance is very low in the useful frequency range. Furthermore, we can simplify the calculation by neglecting the TZA output impedance. Figure 3.10 shows the simplified circuit.

The feedback resistance and capacitance show an impedance:

$$Z_{FB} = \frac{R_{FB}}{1 + sR_{FB}C_{FB}}; [Y_{FB} = \frac{1 + sR_{FB}C_{FB}}{R_{FB}}]$$

(3.1)

Similarly, input inductance and chip card load model are equivalent to an impedance:

$$Z_{IN} = \frac{sL_F}{1 + s^2 L_F C_O}; [Y_{IN} = \frac{1 + s^2 L_F C_O}{sL_F}]$$

(3.2)

The goal of the calculation is to write the TZA transfer function as ratio between output voltage  $V_O$  and input current  $I_{IN}$  generated by a test current source. The first step is to write equations at nodes A and B:

$$A)\dots(V_B - V_A)sC_{INN} = V_A sC_{TZA} + (V_A - V_O)Y_{FB}$$

$$(3.3)$$

$$B)\dots I_{IN} = V_B Y_{IN} + (V_B - V_O)G_F + (V_B - V_A)sC_{INN}$$

(3.4)

Figure 3.7: Input impedance

Figure 3.8: Zoomed input impedance in the useful frequency range

Figure 3.9: Circuit for calculation of the transfer function

Figure 3.10: Simplified schematic for transfer function calculation

From the schematic, it holds that the output voltage is a function of node A voltage across the TZA open loop transfer function:

$$V_O = -A(s)V_A \to V_A = -\frac{V_O}{A(s)}$$

$$(3.5)$$

By substituting (3.5) in the equation relative to node A (3.3), it follows:

$$A)\dots\left(V_B + \frac{V_O}{A(s)}\right)sC_{INN} = -\left(\frac{V_O}{A(s)}\right)sC_{TZA} - \left(\frac{V_O}{A(s)} + V_O\right)Y_{FB}$$

(3.6)

After some algebraic manipulations, we obtain the voltage in B:

$$V_{B} = -V_{O} \left[ \frac{sR_{FB}C_{TZA} + sR_{FB}C_{INN} + 1 + sR_{FB}C_{FB} + A(s) + sR_{FB}C_{FB}A(s)}{R_{FB}A(s)} \right]$$

(3.7)

The same computation can be applied at node B, by substituting (3.5) in the node B equation (3.4), obtaining:

$$I_{IN} = V_B Y_{IN} + (V_B - V_O)G_F + \left(V_B + \frac{V_O}{A(s)}\right)sC_{INN}$$

(3.8)

By substituting (3.7) into (3.8), it follows:

$$I_{IN} = -V_O \left[ \frac{sR_{FB}(C_{TZA} + C_{INN}) + (1 + A(s))(1 + sR_{FB}C_{FB})}{R_{FB}A(s)} \right] \cdot \left( \frac{1 + s^2 L_F C_O}{sL_F} \right) + -V_O G_F \left[ \frac{sR_{FB}(C_{TZA} + C_{INN}) + (1 + A(s))(1 + sR_{FB}C_{FB})}{R_{FB}A(s)} + 1 \right] + +V_O sC_{INN} \left[ \frac{1}{A(s)} - \left[ \frac{sR_{FB}(C_{TZA} + C_{INN}) + (1 + A(s))(1 + sR_{FB}C_{FB})}{R_{FB}A(s)} \right] \right]$$

$$(3.9)$$

Dividing by the output voltage  $V_{O}$  , we get the  $TZ\!A$  transconductance:

$$\frac{I_{IN}}{V_O} = -\left[\frac{sR_{FB}(C_{TZA} + C_{INN}) + (1 + A(s))(1 + sR_{FB}C_{FB})}{R_{FB}A(s)}\right] \cdot \left[\frac{1 + s^2 L_F C_O}{sL_F} + G_F + sC_{INN}\right] - \frac{G_F}{R_{FB}A(s)} + \frac{sC_{INN}}{A(s)} \quad (3.10)$$

For the TZA amplifier, for simplicity, we assume a single pole open loop transfer function:

$$A(s) = \frac{A_{v0}}{1 + \tau s} \tag{3.11}$$

By substituting (3.11) into the transfer function (3.10), we obtain:

$$\frac{I_{IN}}{V_O} = -\left[\frac{sR_{FB}(C_{TZA} + C_{INN}) + \left(1 + \frac{A_{v0}}{1 + \tau s}\right)(1 + sR_{FB}C_{FB})}{R_{FB}A_{v0}}\right] \cdot \left[\frac{1 + sL_FG_F + s^2L_FC_O + s^2L_FC_{INN}}{sL_F}\right](1 + \tau s) + \left[\frac{sR_{FB}C_{INN} - G_F}{R_{FB}A(s)}\right] \quad (3.12)$$

After some algebraic manipulations, it follows:

$$\frac{I_{IN}}{V_O} = -\left[\frac{sR_{FB}(C_{TZA} + C_{INN})(1 + \tau s) + (A_{v0} + 1 + \tau s)(1 + sR_{FB}C_{FB})}{R_{FB}A_{v0}}\right] \cdot \left[\frac{s^2 L_F(C_O + C_{INN}) + sL_FG_F + 1}{sL_F}\right] + \left[\frac{(sR_{FB}C_{INN} - G_F)(1 + \tau s)}{R_{FB}A(s)}\right]$$

(3.13)

Multiplying the factors in brackets at the numerator in (3.13), we obtain the equation:

$$\left[\frac{sR_{FB}(C_{TZA} + C_{INN}) + s^{2}R_{FB}(C_{TZA} + C_{INN})\tau + 1 + sR_{FB}C_{FB} + s\tau}{R_{FB}A_{v0}} + \frac{s^{2}R_{FB}C_{FB}\tau + sR_{FB}C_{FB}A_{v0}}{R_{FB}A_{v0}}\right] \cdot \left[\frac{s^{2}L_{F}(C_{O} + C_{INN}) + sL_{F}G_{F} + 1}{sL_{F}}\right] + \left[\frac{sR_{FB}C_{INN} + s^{2}R_{FB}C_{INN}\tau - G_{F} - sG_{F}\tau}{R_{FB}A_{v0}}\right]$$

(3.14)

To simplify the expressions, we define the variables:

$$C_{\alpha} = C_{INN} + C_{TZA} + C_{FB} \tag{3.15}$$

$$C_{\beta} = C_O + C_{INN} \tag{3.16}$$

Multiplying the factors in brackets at the numerator in (3.14), we have:

$$s^{4}R_{FB}L_{F}C_{\alpha}C_{\beta}\tau + s^{3}R_{FB}L_{F}G_{F}C_{\alpha}\tau + s^{2}R_{FB}C_{\alpha}\tau + s^{3}L_{F}\left[R_{FB}\left(C_{\alpha} + C_{FB}A_{v0}\right) + \tau\right]C_{\beta} + s^{2}L_{F}G_{F}\left[R_{FB}\left(C_{\alpha} + C_{FB}A_{v0}\right) + \tau\right] + s\left[R_{FB}\left(C_{\alpha} + C_{FB}A_{v0}\right) + \tau\right]$$

$$(3.17)$$

while the denominator in (3.14) is:

$$sR_{FB}L_FA_{v0} \tag{3.18}$$

We can further simplify the calculation by defining the variable:

$$X_{\gamma} = [R_{FB} \left( C_{\alpha} + C_{FB} A_{v0} \right) + \tau]$$

(3.19)

Collecting the factors with the same s degrees and adding the factor previously neglected, we obtain:

$$\frac{s^4 R_{FB} L_F C_{\alpha} C_{\beta} \tau + s^3 (R_{FB} L_F G_F C_{\alpha} \tau + L_F X_{\gamma}) + s^2 (R_{FB} C_{\alpha} \tau + L_F G_F X_{\gamma})}{s R_{FB} L_F A_{v0}} + \frac{s R_{FB} L_F A_{v0}}{s R_{FB} L_F A_{v0}} + \frac{s^2 R_{FB} C_{INN} \tau + s (R_{FB} C_{INN} - G_F \tau) - G_F}{R_{FB} A_{v0}}$$

$$(3.20)$$

From (3.20), for the numerator it follows:

$$s^{4}R_{FB}L_{F}C_{\alpha}C_{\beta}\tau + s^{3}L_{F}(R_{FB}G_{F}C_{\alpha}\tau + X_{\gamma}) + s^{2}(R_{FB}C_{\alpha}\tau + L_{F}G_{F}X_{\gamma}) + sX_{\gamma} + s^{3}R_{FB}L_{F}C_{INN}\tau + s^{2}L_{F}(R_{FB}C_{INN} - G_{F}\tau) - sL_{F}G_{F}$$

$$(3.21)$$

while at denominator we have:

$$sR_{FB}L_FA_{v0} \tag{3.22}$$

Finally, we obtain:

$$[NUM] = s^4 R_{FB} L_F C_{\alpha} C_{\beta} \tau + s^3 L_F [R_{FB} (G_F C_{\alpha} + C_{INN}) \tau + X_{\gamma}] + s^2 [R_{FB} C_{\alpha} \tau + L_F [R_{FB} C_{INN} + G_F (X_{\gamma} - \tau)]] + s(X_{\gamma} - L_F G_F)$$

(3.23)

$$[DEN] = sR_{FB}L_FA_{v0} \tag{3.24}$$

$$\frac{I_{IN}}{V_O} = \frac{[NUM]}{[DEN]} = Y \tag{3.25}$$

Since we are interested in the TZA transimpedance, by inverting the last expression, it follows:

$$\frac{V_O}{I_{IN}} = \frac{[DEN]}{[NUM]} = TZA \tag{3.26}$$

which can be written as:

$$\frac{sa_1 + a_0}{s^4b_4 + s^3b_3 + s^2b_2 + sb_1 + b_0} \tag{3.27}$$

$$a_0 = b_0 = 0 \tag{3.28}$$

$$a_1 = R_{FB} L_F A_{v0} \tag{3.29}$$

$$b_1 = X_\gamma - L_F G_F \tag{3.30}$$

$$b_2 = R_{FB}C_{\alpha}\tau + L_F[R_{FB}C_{INN} + G_F(X_{\gamma} - \tau)]$$

(3.31)

$$b_3 = L_F[R_{FB}(G_F C_\alpha + C_{INN})\tau + X_\gamma]$$

(3.32)

$$b_4 = R_{FB} L_F C_\alpha C_\beta \tau \tag{3.33}$$

### 3.4 Small signal analysis

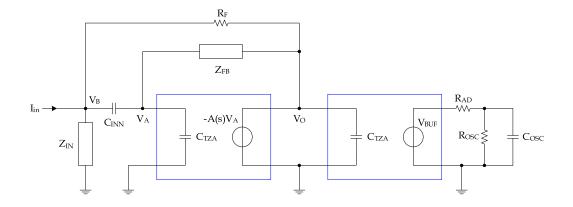

Figure 3.11 shows the small signal circuit, obtained short-circuiting the capacitors. Since the inductor admittance is infinite in the useful range frequency, we can neglect it.

Firstly, we analyze the part of circuit related to output buffer. We want to calculate the buffer transfer function. The node O equation is:

$$O)\dots(v_O - v_B)g_{IBUF} = [v_B - A_{VBUF}(v_O - v_B)]g_{OBUF} + v_B\left(\frac{g_{AD}g_{OSC}}{g_{AD} + g_{OSC}}\right) \quad (3.34)$$

Multiplying the factors we have:

$$v_{O}g_{IBUF} - v_{B}g_{IBUF} = v_{O}g_{OBUF} - v_{O}A_{VBUF}g_{OBUF} + v_{B}A_{VBUF}g_{OBUF} + v_{B}\left(\frac{g_{AD}g_{OSC}}{g_{AD} + g_{OSC}}\right)$$

(3.35)

Figure 3.11: Small signal circuit for SCM second version

By collecting the factors in (3.35), we obtain:

$$v_{O}(g_{IBUF} - g_{OBUF} + A_{VBUF}g_{OBUF}) =$$

=  $v_{B}\left(g_{IBUF} + A_{VBUF}g_{OBUF} + \frac{g_{AD}g_{OSC}}{g_{AD} + G_{OSC}}\right)$  (3.36)

The output buffer's transfer function, which is a voltage gain, is given by the ratio between the output and input voltage. This gain has a value close to 1, as we expect:

$$A_{VBUF}^{CL} = \frac{v_B}{v_O} = \frac{g_{IBUF} + A_{VBUF}g_{OBUF} - g_{OBUF}}{g_{IBUF} + A_{VBUF}g_{OBUF} + \frac{g_{AD}g_{OSC}}{g_{AD} + g_{OSC}}} \cong 1$$

(3.37)

The buffer input impedance is:

$$G_{IBUF}^{CL} = \frac{i_{BUF}}{v_O} = \frac{(v_O - v_B)g_{IBUF}}{v_O}$$

(3.38)

$$G_{IBUF}^{CL} = \left(1 - \frac{v_B}{v_O}\right)g_{IBUF} = \left[1 - \left(\frac{g_{IBUF} + A_{VBUF}g_{OBUF} - g_{OBUF}}{g_{IBUF} + A_{VBUF}g_{OBUF} + \frac{g_{AD}g_{OSC}}{g_{AD} + g_{OSC}}}\right)\right]g_{IBUF}$$

(3.39)

By substituting (3.37) into (3.38), we have:

$$G_{IBUF}^{CL} = \left(\frac{\frac{g_{AD}g_{OSC}}{g_{AD} + g_{OSC}} + g_{OBUF}}{g_{IBUF} + A_{VBUF}g_{OBUF} + \frac{g_{AD}g_{OSC}}{g_{AD} + g_{OSC}}}\right)g_{IBUF}$$

(3.40)

Simplifying the factors at the numerator in (3.40) and looking for the most significant one, with respect to the other factors at denominator, for the buffer input impedance it follows:

$$G_{IBUF}^{CL} \cong \frac{g_{OBUF}g_{IBUF}}{A_{VBUF}g_{OBUF}} = \frac{g_{IBUF}}{A_{VBUF}} \to 0 \Rightarrow R_{IBUF}^{CL} \to \infty$$

(3.41)

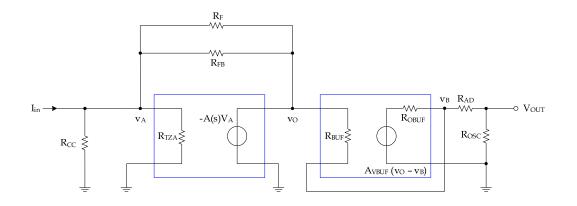

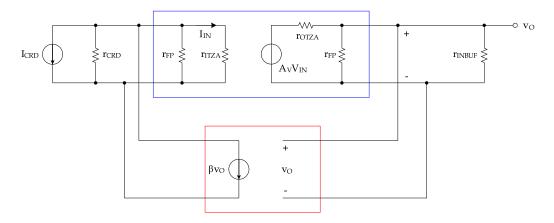

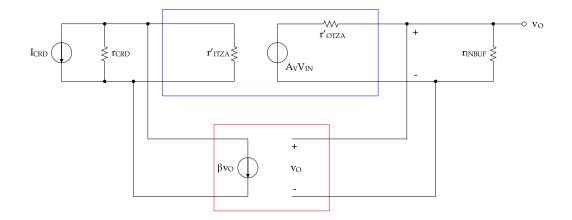

The transimpedance can calculated with reference to a parallel-parallel feedback model, as shown in Figure 3.12.

Figure 3.12: Block model for the parallel-parallel feedback

We can simplify the schematic moving the load effect of the feedback block to the input and output of the direct amplification block. Figure 3.13 shows the new circuit, where:

$$\dot{r}_{ITZA} = r_{ITZA} / / r_{FP} \tag{3.42}$$

$$\dot{r}_{OTZA} = r_{OTZA} / / r_{FP} \tag{3.43}$$

$$\beta = \frac{1}{r_{FP}} \tag{3.44}$$

The transfer function of the new network is calculated starting from the value of output voltage:

$$v_O = A_{VTZA} v_{IN} \left( \frac{r_{FP}}{r_{FP} + r_{OTZA}} \right)$$

(3.45)

The new value for the voltage gain of the direct amplifier is:

$$A_{VTZA}^{'} = \frac{v_{O}}{v_{IN}} = A_{VTZA} \left( \frac{r_{FP}}{r_{FP} + r_{OTZA}} \right)$$

(3.46)

The controlled generator at the output is a function of the input voltage and we have:

Figure 3.13: Schematic block with load effect in the direct amplification block

$$v_{IN} = i_{IN} (r_{FP} / / r_{ITZA})$$

(3.47)

By substituting (3.47) into (3.45), we obtain the new value for the trans - impedance:

$$v_{O} = A_{VTZA} i_{IN} (r_{FP} / / r_{ITZA}) \left( \frac{r_{FP}}{r_{FP} + r_{OTZA}} \right) = A_{VTZA}^{'} i_{IN} (r_{FP} / / r_{ITZA}) \quad (3.48)$$

$$TZA' = \frac{v_O}{i_{IN}} = A'_{VTZA}(r_{FP}//r_{ITZA})$$

(3.49)

The second step of the analysis is the calculation of the output loaded transimpedance, by calculating the output voltage in presence of buffer:

$$v_O = A_{VTZA}^{'} v_{IN} \left( \frac{r_{IBUF}}{r_{OTZA}^{'} + r_{IBUF}} \right)$$

(3.50)

Once again, the new voltage gain value is:

$$A_{VTZA}^{``} = \frac{v_O}{v_{IN}} = A_{VTZA}^{`} \left( \frac{r_{IBUF}}{r_{OTZA}^{`} + r_{IBUF}} \right)$$

(3.51)

By substituting (3.47) in (3.50), we have the loaded transimpedance:

$$v_{O} = A_{VTZA}^{'} i_{IN} (r_{FP} / / r_{ITZA}) \left( \frac{r_{IBUF}}{r_{OTZA}^{'} + r_{IBUF}} \right) = A_{VTZA}^{''} i_{IN} (r_{FP} / / r_{ITZA}) \quad (3.52)$$

$$TZA_{L}^{`} = \frac{v_{O}}{i_{IN}} = A_{VTZA}^{``}(r_{FP}//r_{ITZA}) = A_{VTZA}^{`}\left(\frac{r_{IBUF}}{r_{OTZA}^{`} + r_{IBUF}}\right)(r_{FP}//r_{ITZA}) = TZA^{`}\left(\frac{r_{IBUF}}{r_{OTZA}^{`} + r_{IBUF}}\right)$$

(3.53)

Now we can consider even the input load, which is represented by the chip card resistance. Then we will obtain the new value for the TZA input impedance:

$$r_{_{ITZA}}^{``} = r_{_{ITZA}}^{`} / / r_{_{CRD}}$$

(3.54)

The output voltage is similar to (3.50) and it is obtained by substituting the new gain value (3.51):

$$v_{O} = A_{VTZA}^{'} v_{IN} \left( \frac{r_{IBUF}}{r_{OTZA}^{'} + r_{IBUF}} \right)$$

(3.55)

On the other side, since the input network is a parallel connection, for the TZA input current we have:

$$i_{CRD} = i_{ITZA} r_{ITZA}^{"} + \beta v_O \tag{3.56}$$

$$i_{TZA} = i_{CRD} - \beta v_O \tag{3.57}$$

The TZA input voltage is:

$$v_{\scriptscriptstyle IN} = (i_{\scriptscriptstyle CRD} - \beta v_{\scriptscriptstyle O}) r_{\scriptscriptstyle ITZA}^{``} \tag{3.58}$$

By substituting (3.58) and using the new input impedance value represented by (3.54), for the output voltage it follows:

$$v_{O} = A_{VTZA}^{"} (i_{CRD} - \beta v_{O}) r_{ITZA}^{"} \left( \frac{r_{IBUF}}{r_{IBUF} + r_{OTZA}^{'}} \right)$$

(3.59)

We can separate the factors related to voltage and current. In this way we obtain the new transimpedance value which is close to the total feedback resistance:

$$v_{O}\left[1 + \beta A_{VTZA}^{``}r_{ITZA}^{``}\left(\frac{r_{IBUF}}{r_{IBUF} + r_{OTZA}^{`}}\right)\right] = A_{VTZA}^{``}i_{CRD}r_{ITZA}^{``}\left(\frac{r_{IBUF}}{r_{IBUF} + r_{OTZA}^{`}}\right)$$

(3.60)

$$TZA^{``} = \frac{v_{O}}{i_{CRD}} = \frac{A^{``}_{VTZA}r^{``}_{ITZA}\left(\frac{r_{IBUF}}{r_{IBUF} + r^{`}_{OTZA}}\right)}{1 + \beta A^{``}_{VTZA}r^{``}_{ITZA}\left(\frac{r_{IBUF}}{r_{IBUF} + r^{`}_{OTZA}}\right)} \cong \frac{1}{\beta} = r_{FP}$$

(3.61)

Finally, considering the output matching network, the oscilloscope input voltage is:

$$v_{ICABLE} = v_O \left( \frac{r_{OSC}}{r_{OSC} + r_{AD}} \right) \tag{3.62}$$

The conclusion is that the whole transfer function, with  $r_{\scriptscriptstyle OSC} = r_{\scriptscriptstyle AD},$  is:

$$TZA_{TOT} = \frac{v_{ICABLE}}{i_{CRD}} \cong r_{FP} \left(\frac{r_{OSC}}{r_{OSC} + r_{AD}}\right) = \frac{r_{FP}}{2}$$

(3.63)

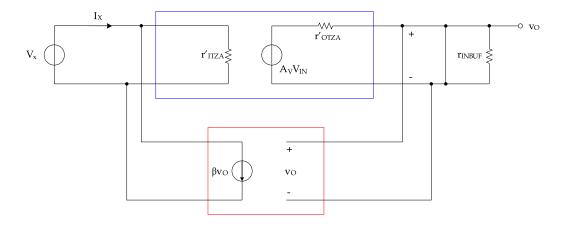

For the TZA closed loop input impedance, we can connect one voltage test source at the input and close with a short circuit the output. Figure 3.14 shows the schematic for the closed loop transfer function calculation.